IBM obtains image of molecule's chemical structure Pg 11

EDN.comment: Keep your hands off my Internet content Pg 4

Signal Integrity Pg 13

Design Ideas Pg 43

Tales from the Cube Pg 58

# VOICE OF THE ENGINEER

OT T

9

0

10

0

OC

Issue 19/2009

www.edn.com

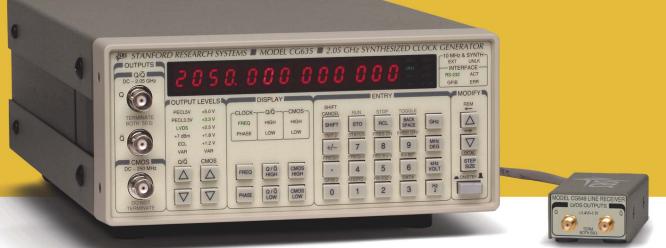

COMPARING COMPARATORS: MEASURE SIGNALS, GET RESULTS

Page 15

15

0

Ð

IP QUALITY LIES BEYOND COMPLIANCE TESTING Page 31

DEEP PACKET INSPECTION OPTIMIZES MOBILE APPLICATIONS Page 37 See the latest LED Drivers from National Semiconductor

www.national.com/led

### FC MODULAR 42-PIN DIP

*Open Frame Product Technology* (actual footprint 65.1mm X 42.5mm)

**DP 12-PIN POWER SIP**

(actual footprint 30.99mm X 20.17mm)

**NORTH AMERICA** +1 800-625-4084

**ASIA PACIFIC** +852 2376-0801

JAPAN +81 (3) 5226-7757

**EUROPE/UK** +44 (0) 1628-891-300

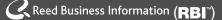

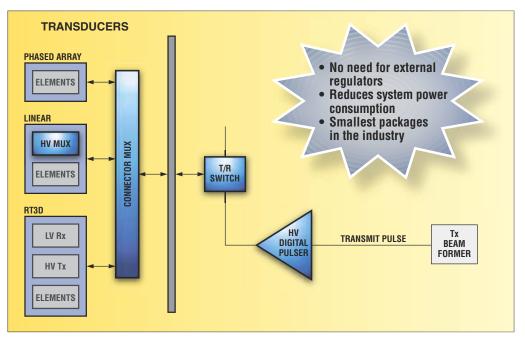

### Small Package Drives Big Speed For Piezo Transducers In Ultrasonic Medical Applications

The PA107DP and MP103FC are the newest additions to the Apex Precision Power® family of high speed, high voltage power amplifiers from Cirrus Logic. The PA107DP is housed in a very small Power SIP measuring less than two inches square. The device targets medical ultrasonic and imaging applications by providing up to 3000 V/µs on voltage supplies up to 200 V. For applications requiring lower speeds, but multiple drivers, the MP103FC is a dual channel amplifier

with a high power bandwidth of 230 kHz, or a 180 V/ $\mu$ s slew rate. The open frame form factor of the MP103FC is ideal for high speed assembly and provides a low per unit cost in comparison with many in-house discrete designs.

| Model   | Slew<br>Rate | Output<br>Current            | Supply Voltage<br>Operation  |

|---------|--------------|------------------------------|------------------------------|

| PA107DP | 3000 V/µs    | 1.5 A continuous<br>5 A Peak | 40 V to 200 V<br>Dual Supply |

| MP103FC | 180 V/µs     | Up To<br>15 A PEAK           | 30 V to 200 V<br>Dual Supply |

CIRRUS LOGIC®

DOWNLOAD A COPY OF THE CIRRUS LOGIC V15 APEX PRECISION POWER® PRODUCT DATA BOOK AT WWW.CIRRUS.COM/107EDN

ir i

For product selection assistance or technical support with Apex Precision Power® products call 1-800-546-2739 or apex.support@cirrus.com.

© 2009 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus, the Cirrus Logic logo designs, Apex Precision Power, Apex and the Apex Precision Power logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners. EDN 10082009

Over 400,000 products in stock from more than 400 supplier partners:

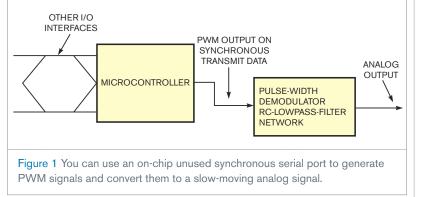

An additional 1,000,000+ components can be sourced at digikey.com

The industry's broadest product selection available for immediate delivery

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2009 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# EDN 10.8.09 contents

## Designing an accessible board

24 Design in access to verification and debugging during-not afterthe development of a board-level product.

by Ron Wilson, Executive Editor

### Comparing comparators: Measure signals, get results

15 Simple in concept, voltage comparators have myriad specifications that complicate their application.

by Paul Rako, Technical Editor

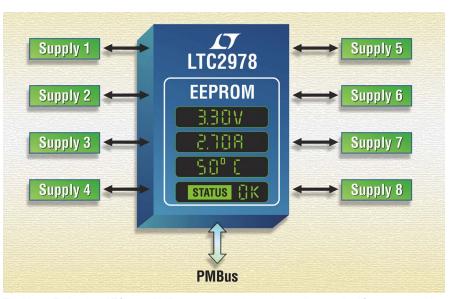

- 7 Octal power-converter-control chip uses PMBus

- 8 ADC modules have onboard FPGAs for speedy data analysis

- 9 Precision JFET op amp operates with 36V power

- 9 DSP engine sports hybrid-SIMD/VLIW operation with ITU compatibility

- 9 High hot/cold factor boosts HB-LED efficacy

- 10 Cadence links FPGA-pin allocation to PCB-layout tools

- 10 Fijitsu launches USB 3.0to-SATA-bridge chip

- 11 **Research Update:** DNA scaffolding targets sub-22nm lithography; IBM obtains image of modecule's chemical structure

## IP quality lies beyond compliance testing

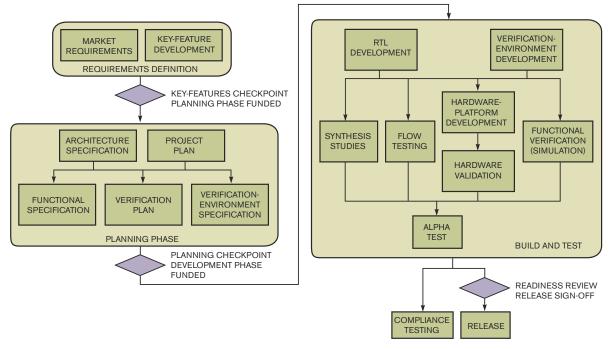

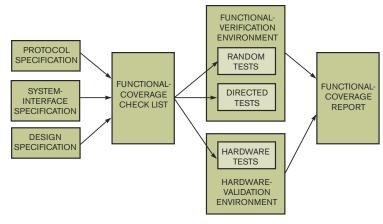

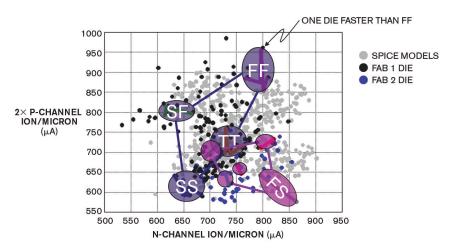

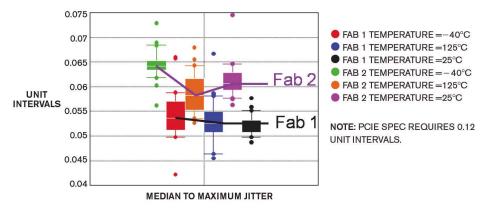

31 Of course you want your standard-interface IP to pass compliance testing. But that accomplishment is just the beginning. Complete quality assurance for IP cores has far more challenges.

by Navraj Nandra, Synopsys Inc

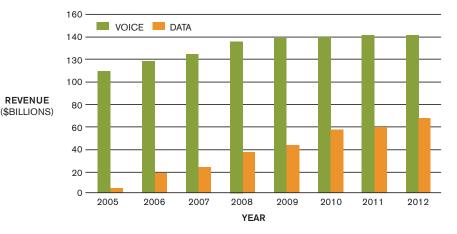

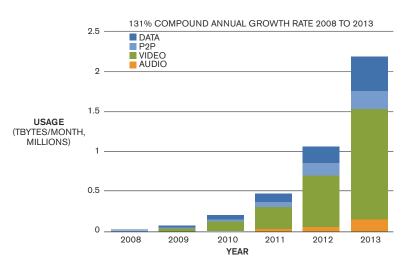

### Deep packet inspection optimizes mobile applications

37 Mobile data provides a notable growth opportunity for cellular operators, but adoption will be slow unless networks can provide good service to all subscribers. Deep packet inspection enables operators to understand the applications their subscribers are using and to build appropriate networks. by Mike Coward, Continuous Computing

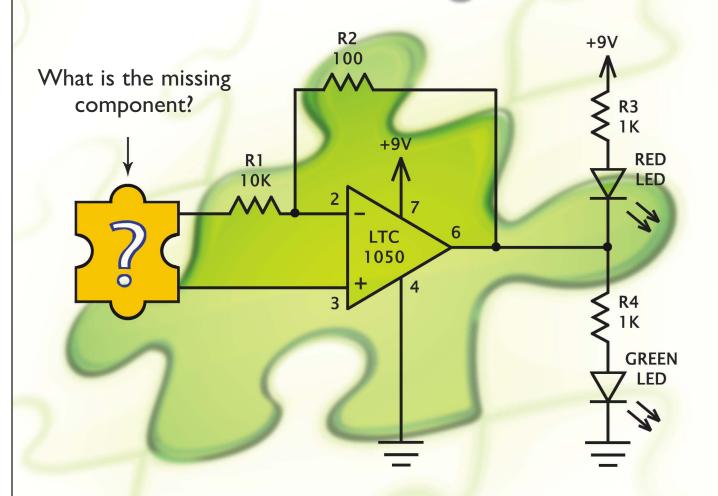

## DESIGNIDEAS

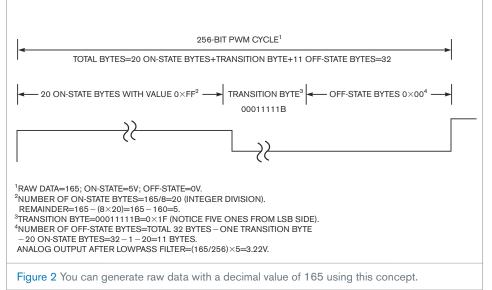

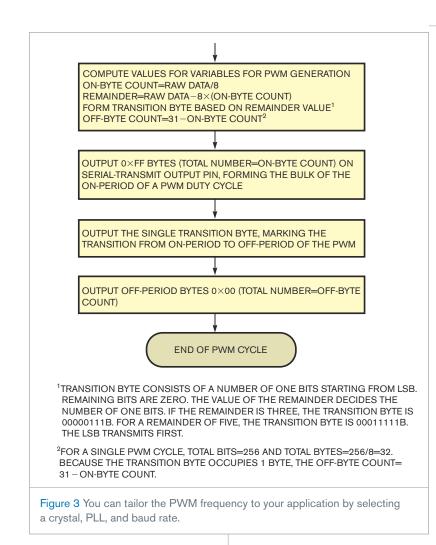

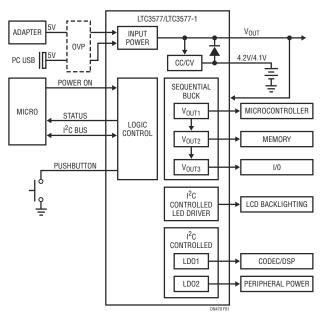

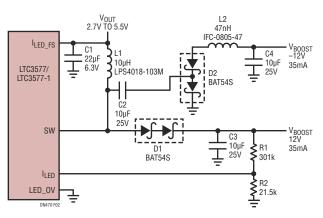

43 Unused port adds a PWM/analog channel to a microcontroller

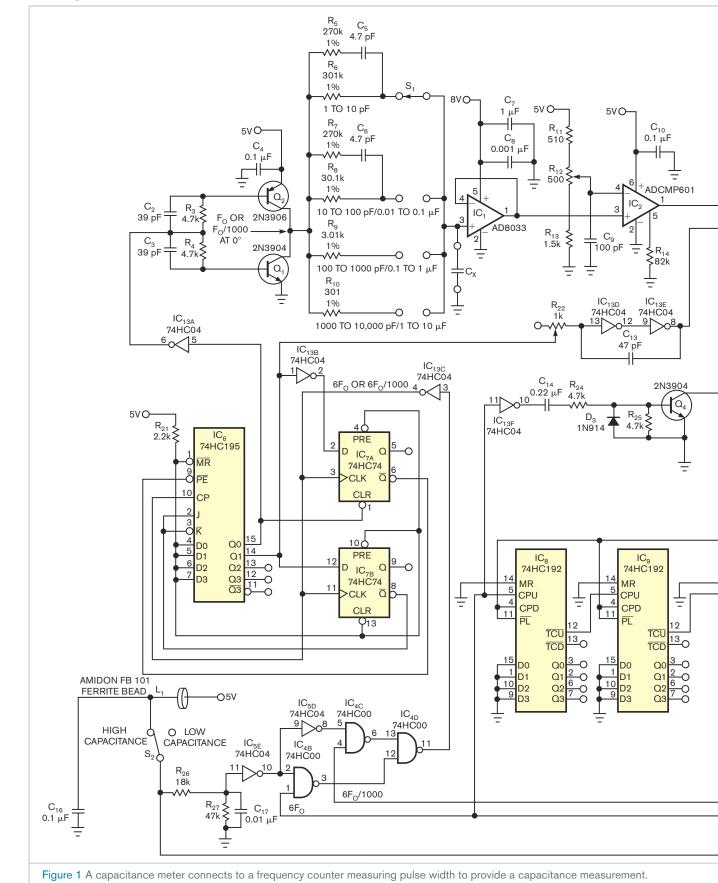

44 Capacitance meter uses PLL for high accuracy

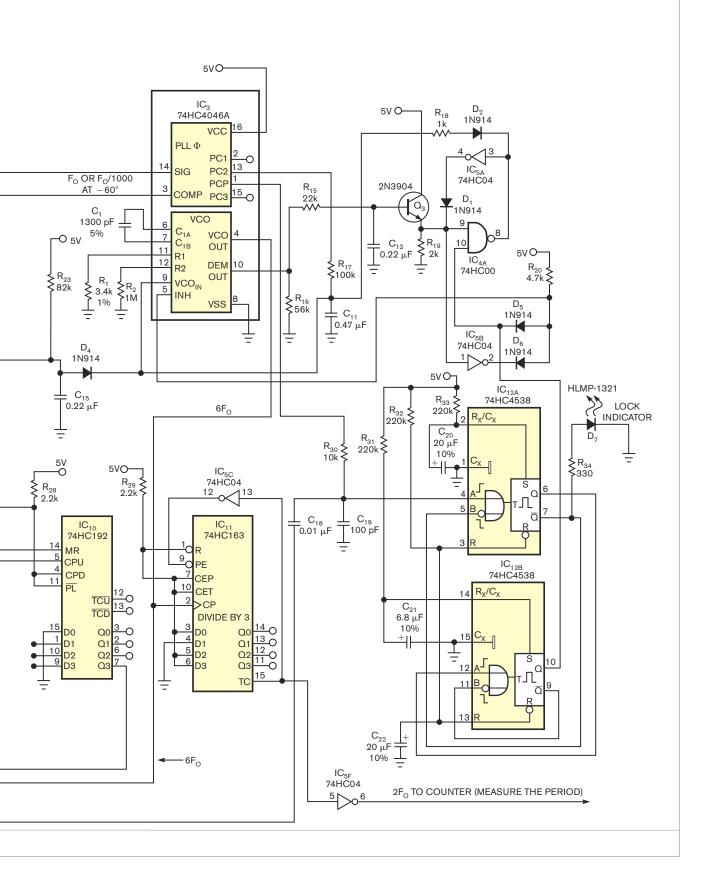

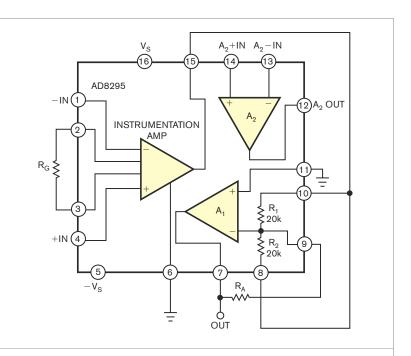

50 Resistor compensates for instrumentation-amp gain drift

Send your Design Ideas to edndesignideas@reedbusiness.com.

### **DEPARTMENTS & COLUMNS**

- 4 EDN.comment: Keep your hands off my Internet content

- 13 Signal Integrity: Real signals

- 54 Supply Chain: With spotlight on Asia/Pacific, don't forget Americas design; CPE market sees some bright spots; European Union, other organizations propose 15 "substances of very high concern"

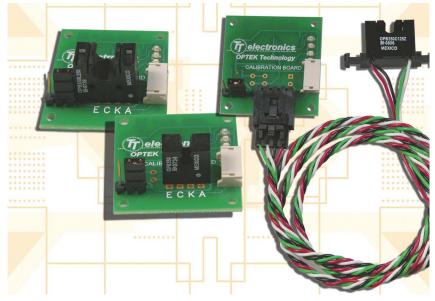

- 56 **Product Roundup:** Sensors and Transducers, Computers and Peripherals

- 58 **Tales from the Cube:** Keep it simple, stupid, and kiss problems goodbye

### **EDN** online contents

### ONLINE ONLY

Check out these Web-exclusive articles:

### Thermal-design guidelines for solid-state lighting applications using LEDs

Six critical steps are necessary to developing a successful, cost-effective thermal design for an LED application. →www.edn.com/article/CA6695956

www.edn.com/article/CA0090900

### FPGA architectural power-saving techniques at 40 nm

As geometries shrink, FPGAs must begin to employ design-specific power-management techniques to save power while meeting timing.

→www.edn.com/article/CA6698462

## www.edn.com

Here is a selection of recent articles receiving high traffic on www.edn.com.

Take advantage of open-source hardware

→www.edn.com/article/CA6676116

Missing pulse detects position or produces a delay

→www.edn.com/article/CA6694947

Is there gold in green technology? A microelectronics perspective

→www.edn.com/article/CA6697713

Solar market to recover ... eventually

→www.edn.com/article/CA6696791

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Bivd, Highlands Ranch, CO 80129-2345, Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, Chief Executive Officer, Jeff DeBalko, President, Business Media. Periodicals postage paid at Littlevon, CO 80128-345. Telephone (303) 470-4445. Circulation records are maintained at Reed Business Information, 8878 S Barrons Bivd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% GST, GST#123397457); Mexico, \$229.99 one year; air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN ®, 8878 S Barrons Bivd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 54, Number 19 (Printed in USA).

## Benchmark MOSFETs

Same Package, 60% More Current

### **Logic Level**

| Part<br>Number    | B <sub>VDSS</sub><br>(V) | R <sub>DS(on)</sub><br>4.5Vgs<br>(mΩ) | Q <sub>G</sub><br>4.5Vgs<br>(nc) | I <sub>D</sub> @<br>25°C<br>(A) | Package |  |  |  |

|-------------------|--------------------------|---------------------------------------|----------------------------------|---------------------------------|---------|--|--|--|

| IRLS3034-7PPBF    | 40                       | 1.7                                   | 108                              | 240*                            | D2PAK-7 |  |  |  |

| IRLB3034PBF       | 40                       | 2.0                                   | 108                              | 195*                            | T0-220  |  |  |  |

| IRLS3034PBF       | 40                       | 2.0                                   | 108                              | 195*                            | D2PAK   |  |  |  |

| IRLS3036-7PPBF    | 60                       | 2.2                                   | 91                               | 240*                            | D2PAK-7 |  |  |  |

| IRLB3036PBF       | 60                       | 2.8                                   | 91                               | 195*                            | T0-220  |  |  |  |

| IRLS3036PBF       | 60                       | 2.8                                   | 91                               | 195*                            | D2PAK   |  |  |  |

| IRLS4030-7PPBF    | 100                      | 4.1                                   | 87                               | 190                             | D2PAK-7 |  |  |  |

| IRLB4030PBF       | 100                      | 4.5                                   | 87                               | 180                             | T0-220  |  |  |  |

| IRLS4030PBF       | 100                      | 4.5                                   | 87                               | 180                             | D2PAK   |  |  |  |

| * Package limited |                          |                                       |                                  |                                 |         |  |  |  |

### **Features**

- Suited for industrial battery, power supply, high power DC motors, and power tools

- Industrial grade and MSL1

- RoHS compliant

Your FIRST CHOICE for Performance

For more information call 1.800.981.8699 or visit www.irf.com

### BY RICK NELSON, EDITOR-IN-CHIEF

# Keep your hands off my Internet content

he US Congress should promptly pass HR3458—the Internet Freedom Preservation Act of 2009. Despite the whining of the badly misnamed Hands off the Internet organization, passage of the act is necessary to ensure a level playing field for content providers and consumers, no matter how big or how small. Net neutrality is critical to ensuring that consumers, not deep-pocketed content providers in secret deals with service providers, determine what content they want to access.

Net-neutrality opponents—the marketers and financiers concocting schemes to charge a premium for faster content delivery—need to get out of the way and let their engineers deliver the bandwidth necessary to ensure that everyone's content gets through without discrimination. It shouldn't take a presidential address to a joint session of Congress to get Congress to tell net-neutrality opponents to "keep your hands off my Internet content."

As a recent editorial (**Reference 1**) points out, "On the Internet today, a Web site run by a solo blogger can load as quickly as any corporate home page. Internet-service providers, including leading cable and phone companies, want to be able to change that [situation] so they can give priority to businesses that pay, or make deals with, them." That scenario should not happen. As the editorial notes, without net neutrality, businesses could slow down or block Web content from competitors or content advocating for political or social causes. That issue is not a hypothetical one, the editorial notes.

The arguments of Hands off the Internet are disingenuous at best. The organization cites the development of high-speed Internet-access systems including cable wire, DSL (digital-subscriber line), and wireless, saying the developments resulted from "competition in its purest form." OK, but so what? They should apply that developmental expertise to building sufficient bandwidth that they need not ration it. And HR3458 makes absolutely no mention of transmission media, so what's the point of the example?

What does the bill say, specifically? In a nutshell, providers may not discriminate against anyone's ability to transmit or receive content, may not impose any charge beyond user end charges, may not prevent a user from attaching any device to the network as long as the device does not harm the network, must offer Internet access to any person, and may not prioritize one provider's traffic over another's.

One issue that net-neutrality opponents harp on is telemedicine. Here is what the bill says: "Reasonable Network Management—Nothing ... shall be construed to prohibit an Internet-access provider from engaging in reasonable network management consistent with the policies and duties of nondiscrimination and openness set forth in this Act ... a network-management practice is a reasonable practice only if it furthers a critically important interest, is narrowly tailored to further that interest, and is the means of furthering that interest that is the least restrictive, least discriminatory, and least constricting of consumer choice available." Does anyone reasonable think that telemedicine—at least for those who have the health insurance that might actually pay for it isn't a "critically important interest"?

What's most appalling about net neutrality's opponents is their "can'tdo" attitude. They can't possibly provide all the bandwidth consumers want, so they'll have to limit traffic except that of their "friends." In fact, In-Stat (www.instat.com) recently reported that in the US download speeds are improving and consumers are generally satisfied with the speed of their current broadband connections.

What's happening here is that the marketers, financiers, and lawyers within the companies that oppose net neutrality want to do for the Internet what "financial engineers" did for the economy. It's time for Congress to pass HR3458 and tell opponents to "keep your hands off consumers' Internet-content preferences." Then, let real engineers step up and deliver the necessary bandwidth.

Visit my blog at http://bit.ly/sGJ6r to comment and to find links to source material.**EDN**

### REFERENCE

"Access and the Internet," The New York Times, Aug 29, 2009, www.nytimes.com/2009/08/29/ opinion/29sat3.html.

> Contact me at rnelson@ reedbusiness.com.

### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes 1-925-736-7617; judy.hayes@reedbusiness.com

#### VICE PRESIDENT, INTERACTIVE MEDIA

AND SALES MANAGEMENT Karthik Krishnan 1-646-746-7580; karthik.krishnan@reedbusiness.com

#### EDITOR-IN-CHIEF. EDN WORLDWIDE

Rick Nelson 1-781-734-8418; rnelson@reedbusiness.com

### EXECUTIVE EDITOR

Ron Wilson 1-510-744-1263; ronald.wilson@reedbusiness.com

### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

#### NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

*EDN.* 225 Wyman St, Waltham, MA 02451. **www.edn.com**. Phone 1-781-734-8000. **Address changes or subscription inquiries:** phone 1-800-446-6551; fax 1-303-470-4280; subsmail@ reedbusiness.com. For a free subscription, go to **www.getfreemag.com/edn**. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

EDITORIAL/WEB PRODUCTION Diane Malone Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198

Melissa Annand Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279

Adam Odoardi Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> **CONSULTING EDITOR** Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp Surface Mount and Plug-In 400 / 800 Hz

# Transformers

- 0.4 Watts to 150 Watts

Power Transformers

- 115V/26V-400/800 Hz Primary

- Secondary Voltages 2.5V to 300V

- Manufactured to MIL-PRF 27 Grade 5, Class S, (Class V, 155°C available)

- Surface Mount or Plug-In

- Smallest possible size

See Pico's full Catalog immediately www.picoelectronics.com

### **PICO** Electronics, Inc

143 Sparks Ave., Pelham, NY 10803

Call Toll Free: 800-431-1064

E Mail: info@picoelectronics.com FAX: 914-738-8225

Delivery - Stock to one week INDUSTRIAL • COTS • MILITARY

## MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

# EDITED BY FRAN GRANVILLE STATE OF THE STATE

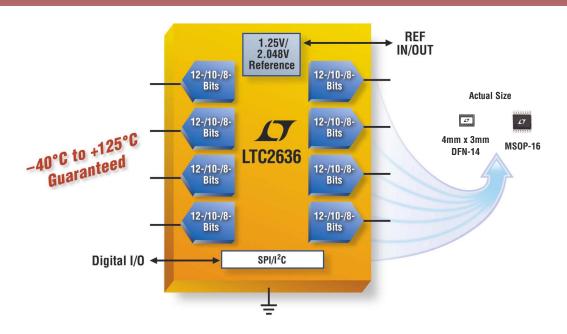

# Octal power-converter-control chip uses PMBus

inear Technology Corp's new LTC2978 monitoring-and-control chip supervises eight switching power converters. You communicate with the IC over the PMBus (power-management bus). The controlled supplies have output voltages of 0 to 6V. The device has an onboard EEPROM that stores settings when the chip is off. Eight 10bit DACs use the power converter's trim pin or resistor-feedback network to sequence, adjust, and margin the eight target converter chips. The device measures the target converter's output voltage by multiplexing a 15-bit deltasigma ADC across the eight converters. The ADC can also measure the part's input voltage. A carefully trimmed onboard 1.232V reference provides a ±0.25% overall accurate measure-

ment, including ADC errors. The device operates from a 4.5 to 12V power supply and contains 2.5 and 3.3V linear regulators. It also has an internal temperature sensor. You can cascade multiple devices if you need to control more than eight converters.

The LTC2978 allows you to bring eight analog- or digitalpower-converter chips under PMBus control. It can perform as a watchdog timer, a sequencer, and a supervisor to monitor both overvoltage and undervoltage events. You can also use the part to perform margining of the target power supplies during manufacturing to ensure that your system works properly under a predetermined range of converter supply voltages. The chip logs faults to the internal EEPROM. The chip's interface and command set comply with the PMBus specification and operate as fast as 400 kHz. You can explore all of the product's features with LTpowerPlay, a free software package that can communicate over the PMBus. The demoboard kit includes a dongle to convert your computer's USB port to an SMBus (systemmanagement bus).

The LTC2978 comes in a  $9 \times 9$ -mm, 64pin QFN package. The LTC2978CUP version operates at a 0 to  $+70^{\circ}$ C junction temperature, and the LTC2978IUP version operates in the -40 to  $+85^{\circ}$ C range. The commercial-temperature version sells for \$10.95 (1000).

>Linear Technology Corp, www.linear.com.

### FEEDBACK LOOP

"It seems appropriate to the idea of replacing the old whistling kettle with a softwaredriven alternative. Who can forget Lauren Bacall's immortal quote? 'You know how to whistle, don't you, Steve? You just put your lips together—and blow.""

—Engineer Gary Fisher, in *EDN*'s Feedback Loop, at www.edn. com/article/CA6674029. Add your comments.

-by Paul Rako

The Linear Technology LTC2978 PMBus power-supply-monitor and -controller IC manages and supervises eight regulators using a trim pin or feedback resistors.

# pulse

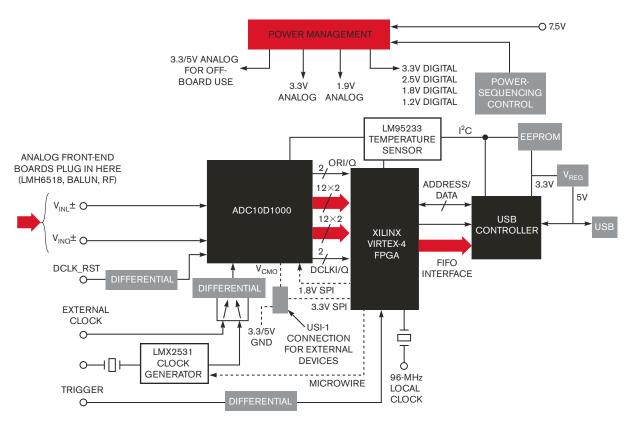

### ADC modules have onboard FPGAs for speedy data analysis

gilent's Acqiris product group recently announced three highspeed, high-accuracy, wide-dynamic-range, modular digitizers targeting medical imaging, scientific instrumentation, nondestructive testing, storage testing, LIDAR (light detection and ranging), validation of mixedsignal semiconductors in automated test equipment, and advanced research in high-energy physics, nuclear physics, and astrophysics.

The four-channel, 12-bit SVM3500 digitizer allows channel interleaving that enables acquisition at rates to 2G samples/sec. The module focuses on applications in radar, EW (electronic warfare), and SI (synthesized instrumentation). The input-amplifier bandwidth is more than twice the minimum for accurate reproduction of signals that you can digitize without aliasing at 2G samples/sec.

The unit adds an analog-digitizer mezzanine board, which includes four 12-bit, 500Msample/sec ADCs, to the manufacturer's U1083A VME/VXS base module. Also on the mezzanine board is the MCK clockdistribution circuit, which distributes throughout the board very-low-added-jitter in-phase, quadrature, or out-of-phase

The U1084A PCIe module outputs data at 650 Mbytes/sec.

versions of an external clock. These clock signals allow interleaved acquisition at rates to 2G samples/sec. In the interleaved mode, an FIR (finite-impulse-response) filter in an onmezzanine Xilinx (www.xilinx. com) Virtex-5 FPGA corrects for static offset and gain errors and frequency-dependent gain and delay mismatch among the ADCs. This FPGA also includes an externally accessible look-up table. The resulting analog performance maintains more than 10 effective bits over a 10-MHz to 1-GHz band. Features include an SFDR (spurious-free dynamic range) to 80 dBc at 500M samples/sec and 70 dBc at 2G samples/sec, THD (total harmonic distortion) of -80 dBc at 500M samples/sec and -79 dBc at 2G samples/sec, and SNR (signal-to-noise ratio) greater than 62 dBc.

The base card provides

high-performance, real-time data processing by means of the large SX55 and FX100 Xilinx Virtex-4 FPGAs. The board supports eight 3.125-Gbps serial links on the VXS backplane. Two optical links on the front panel support data transfers at rates to 3.125 Gbps, making the aggregate data bandwidth more than 3.5G bytes/sec. The VME64x interface supports the 2eSST (twoedge-source-synchronoustransfer) protocol. The optional FDK (firmware-development kit) helps you develop applications for the SX55 and FX100 FPGAs. The FDK includes a set of cores that interface to the hardware, a base design to provide ready-to-use designs, and a test-bench environment.

The dual-channel, highspeed, 8-bit, four-lane U1084A PCIe (Peripheral Component Interconnect Express) digitizer acquires as many as 4G

samples/sec. This digitizer with an onboard FPGA offers a 1.5-GHz bandwidth and incorporates a 15-psec TTI (triggertime interpolator) for accurate timing measurement. The FPGA-based peak-detection and -analysis firmware provides real-time signal processing and allows real-time acquisition and peak detection at data rates to 4G samples/sec.

Firmware options allow the data-converter card to perform user-defined postprocessing tasks, which you can easily upload into the FPGA under program control. These tasks can redefine the way in which the card acquires and processes data, making the system flexible and easy to reconfigure. The signal-peak-detection firmware option enables the board to create a peak histogram of successive acquisitions, with each histogram bin containing peak counts or summed peak amplitudes. The unit can record as many as 60M peaks/ sec and exhibits trigger jitter of just 250 psec. With the highspeed PCIe bus, the onboard processing maximizes data and measurement throughput. The digitizer outputs data at rates to 650 Mbytes/sec. Software drivers for Windows and Linux enable you to easily integrate the U1084A into measurement systems or use it to replace other high-speed Acqiris data converters.

Single-unit prices begin at \$26,500 for the U1084A, \$46,000 for the SVM3500 (U1083A-005), and \$42,000 for the SVM4800 (U1083A-007). For more, go to www. edn.com/article/CA6697248. -by Dan Strassberg

### Agilent Technologies, www.agilent.com/find/ digitizers, www.agilent.com/ find/u1084a, www.agilent.

### **DILBERT By Scott Adams**

### Precision JFET op amp operates with 36V power

nalog Devices' new ADA4627 JFET operational amplifier has 5-pA maximum bias current at 25°C and 500-pA maximum current at -40 to +85°C. The 19-MHz-bandwidth, A-grade part has less than 300-µV maximum offset voltage and  $2-\mu V/^{\circ}C$ maximum offset drift. The B-grade part has 200 µV of maximum offset and  $1-\mu V/$ °C drift. The device achieves an 82V/µsec slew rate and has an open-loop gain of 120 dB. The output drives loads as low as  $600\Omega$ . Analog Devices built the device with the dielectrically isolated iPolar

process technology, which enables  $5.5\text{-nV}/\sqrt{\text{Hz}}$  voltage noise when operating on  $\pm 18V$  rails. Voltage noise at 10 Hz is  $16.5 \text{ nV}/\sqrt{\text{Hz}}$ .

Because JFETs are buried devices, they are not subject to noise that surface defects create. The drawback is that diffusion rather than lithography controls JFET specs, complicating the manufacture of precision devices with low offset voltage. The combination of low noise, low bias current, and high precision makes the ADA4627 suitable for circuits that require accurate signal acquisition and fast settling in optical, communications, and high-speed data-acquisition systems; professional audio and test equipment; and medical instrumentation. The device can also act as an output buffer in a DAC or as an amplifier for high-sourceimpedance sensors and photodiodes.

The ADA4627 comes in eight-pin SOIC packages and  $3\times3$ -mm, eight-pin LFCSPs. It operates over a temperature range of -40 to  $+125^{\circ}$ C. The \$6.75 (1000), A-grade part is inferior to the B-grade part, which costs \$10.75 (1000).

-by Paul Rako Analog Devices, www. analog.com.

### HIGH HOT/COLD FACTOR BOOSTS HB-LED EFFICACY

Philips' new Luxeon Rebel HB LEDs (high-brightness light-emitting diodes) have a 0.93 hot/cold factor-the ratio of junction temperatures at 100 and 25°C. The new devices thus beat typical specs for production LEDs, whose hot/cold factors range from 0.8 to 0.85. These factors are important in applications such as light-fixture luminaires, which spend most of their time operating at temperatures of 80 to 110°C-much higher than the 25°C junction temperature that most HB-LED spec sheets give as the light output. As its junction temperature increases, an LED's light output and efficacy decrease.

-by Margery Conner Philips Lumileds, www. philipslumileds.com.

The hot/cold factor-the ratio of junction temperatures at 100 and 25°C-is 0.93 for Philips' new Luxeon Rebel LED.

The ADA4627 JFET op amp features low offset, low drift, and low input bias current.

### DSP engine sports hybrid-SIMD/VLIW operation with ITU compatibility

Tensilica's 16-bit dual-MAC (multiply/accumulate) ConnX D2 DSP engine integrates with the company's Xtensa LX processor core. The DSP core supports modeless switching between SIMD (single-instruction/multiple-data) and VLIW (very-long-instruction-word) formats. The VLIW format supports two pipeline executions, in which one may be an SIMD operation, with register moves and operations such as autoincrement loads. The DSP engine provides 1-to-1 mapping support for ITU-T (www.itu. int) reference-code intrinsics, as well as 1-to-1 mapping to most intrinsics for Texas Instruments' (www.ti.com) C6x family. The ConnX D2 engine primarily targets the telecom infrastructure and VOIP (voice-over-Internet Protocol) applications.

The ConnX D2 DSP-engine option adds dual 16-bit MAC units and an eight-entry, 40-bit register file to the base architecture of the Xtensa LX DPU (data-plane-processing unit). It supports 16-, 32-, and 40-bit integer and fixed-point, 16-bit complex, and 8- and 16-bit vector data types, as well as seven addressing modes. For more on this product, go to www.edn. com/article/CA6685704.—**by Robert Cravotta** ▷**Tensilica**, www.tensilica.com.

# pulse

# Cadence links FPGA-pin allocation to PCB-layout tools

Designers who use today's large FPGAs on their PCBs (printed-circuit boards) face an increasing problem: handling the pinout and board tracking around the packages of these programmable devices. The FPGAs have large pinouts; they offer considerable flexibility in allocation of pins to internal logic functions but also have complex rules that you must follow when doing so.

FPGA designers typically accomplish this task with minimal knowledge of the connectivity of those pins to other packages on the PCB. Other engineers develop the overall circuit functions, connecting the FPGA to processors, memory, and other packages. The job of creating the PCB layout falls to yet other engineers, who must find escape routes for all the signal groups that emerge from the FPGA and route them to other packages. Those engineers must also account for features such as wide memory buses and fast signal lines.

To address these problems, Cadence has incorporated into its Allegro and OrCAD products software from Taray (www.tarayinc.com). The Taray software provides automated assistance in the FPGA-pinallocation step, yielding a correct-by-construction process. The process, automated placement-aware FPGA-pin-I/Oassignment synthesis, gives the software knowledge of the pin-allocation rules for Xilinx (www.xilinx.com) and Altera (www.altera.com) FPGAs and of the connectivity of the logic function in the FPGAs to other packages.

Large FPGAs contain so

much logic that it is difficult to represent their functions in an understandable form on one diagram, so engineers view different functions on different pages and lose sight of the bigger picture. The Taray tool tracks that information; it also allows you to make a generic placement of packages on a "canvas" when performing initial PCB design, and it yields a global view of connectivity and connection density. It further avoids manual errors in the pinallocation step.

The offering is applicable whether you are designing an FPGA-based board as a final product or building an ASIC prototype in which the logic of the target device is divided among many complex FPGAs. Using the Taray/Allegro tool greatly simplifies such designs because the process that fragments the logic onto the FPGAs has no knowledge of placement or layout. With the new software, you can automate pin assignment across all of the FPGAs in one step.

The ability to quickly view an optimized placement for any given logic architecture also permits you to explore costversus-performance tradeoffs at the board-design level. Under the Cadence PCBtool brands, the software is available for the Version 16.2 release as OrCAD FPGA System Planner or Allegro FPGA System Planner L, XL, and GXL tiers, and it integrates tightly with OrCAD Capture, OrCAD PCB Designer, Allegro Design Entry HDL (hardwaredesign language), and Allegro PCB Design products. Taray also continues to sell its tool offering, 7Circuits, as a standalone product.

-by Graham Prophet Cadence Design Systems, www.cadence.com.

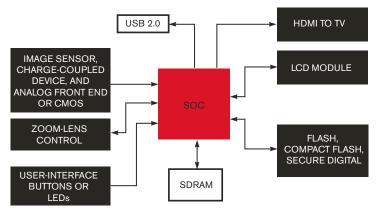

### FUJITSU LAUNCHES USB 3.0-TO-SATA-BRIDGE CHIP

Fujitsu Microelectronics recently announced a 3.0-to-SATA (serial-advanced-technology-attachment)-bridge chip. The company intends the device to act as a connection between a USB (Universal Serial Bus) 3.0 cable and a SATA external-storage device. It incorporates an AES (Advanced Encryption Standard) engine-critical to many external-media applications-and Fujitsu claims that the chip can support 300-Mbyte/sec throughput with flowthrough encryption/decryption.

The device includes USB 3.0 Revision 1.0 and 2.0 PHY (physical)- and link-layer blocks and has 3-Gbps SATA Gen 2i PHY and link layers. Structurally, the chip includes an internal bus for data movement, the AES engine, and an unspecified 32-bit microprocessor core with attendant SRAM. The CPU's job is primarily system-control functions within the chip, such as initialization, dispatching tasks to the AES engine, and handling the interventionrequired bits of the two link-layer protocols. The RAM is for code and data storage for the CPU rather than for buffering, according to Davy Yoshida, Fujitsu's director of business development. The chip also includes an SPI (serial-peripheral-interface) port to an external serial-flash chip for boot-loading of code and some general-purpose I/O pins for status LEDs and other functions.

The chip requires both 1.2 and 3.3V supplies and typically consumes 550 mW. That requirement means that a bus-powered interface with a local regulator to step the USB supply pin down to the required voltages would eat up most of the allowed 900 mA during operation without passing any power on to the mass-storage device. So interfaces using the chip will require an external power supply, probably one that the storage device furnishes. Further, according to Fujitsu, the chip's USB I/O pins do not tolerate high voltage, so they may require external protection circuitry to comply with the letter of the 3.0 specification about tolerating shorts to the power pin.

Fujitsu is looking at applications in both automotive infotainment and consumer electronics. So don't be surprised to see the company's PHY surface soon in some additional bridge chips, and perhaps in 40-nm form, in forthcoming consumer and automotive SOCs (systems on chips). For more on this development, go to www.edn. com/091008pa.—by Ron Wilson

Fujitsu, www.fujitsu.com.

10.08.09

### **RESEARCH UPDATE** BY SUZANNE DEFFREE

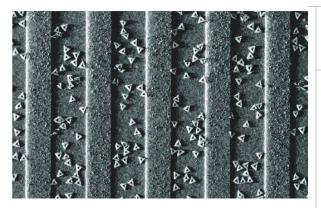

# DNA scaffolding targets sub-22-nm lithography

Cientists at IBM Research and the California Institute of Technology (Pasadena, CA) have discovered an advancement that could be a major step forward in the semiconductor industry's move to sub-22nm lithography. IBM researchers and collaborator Paul WK Rothemund of Caltech are discussing a development in combining lithographic patterning with self-assembly, a method of arranging "DNAorigami" structures on surfaces compatible with today's semiconductor-manufacturing equipment.

IBM says that its approach of using DNA molecules as scaffolding may provide a way to reach sub-22-nm lithography. IBM describes the scaffolding as a procedure in which millions of carbon nanotubes could self-assemble into precise patterns by sticking to DNA molecules.

The positioned DNA nanostructures can serve as scaffolds, or miniature PCB (printed-circuit boards), for the assembly of components, such as carbon nanotubes, nanowires, and nanoparticles, at dimensions significantly smaller than possible with conventional semiconductor-fabrication techniques.

The techniques for preparing DNA origami, which scientists at Caltech developed, cause single DNA molecules to selfassemble in a solution using a Low concentrations of triangular DNA origami bind to wide lines on a lithographically patterned surface (courtesy IBM).

reaction between a long strand of viral DNA and a mixture of short, synthetic oligonucleotide strands. These short segments act as staples, folding the viral DNA into the desired 2-D shape through complementary base-pair binding. Scientists can modify the short staples to provide attachment sites for nanoscale components at resolutions as small as 6 nm. In this way, scientists can prepare DNA nanostructures, such as squares, triangles, and stars, with dimensions of 100 to 150 nm per edge and a thickness the width of the DNA double helix

IBM uses traditional semiconductor techniques to etch out patterns and uses either electron-beam or optical lithography to create arrays of binding sites of the proper size and shape to match those of individual origami structures. The researchers say that the discovery of the template material and deposition conditions were the keys to affording high selectivity so that origami binds only to the patterns of sticky patches and nowhere else (**Reference 1**).

### REFERENCE

1 Kershner, Ryan J, Luisa D Bozano, Christine M Micheel, Albert M Hung, Ann R Fornof, Jennifer N Cha, Charles T Rettner, Marco Bersani, Jane Frommer, Paul WK Rothemund, and Gregory M Wallraff, "Placement and orientation of individual DNA shapes on lithographically patterned surfaces," Nature Nanotechnology, September 2009, www.nature. com/nnano/journal/v4/n9/ pdf/nnano.2009.220.pdf.

▶**IBM Research**, www. research.ibm.com.

California Institute of Technology, www.caltech. edu.

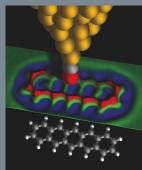

### IBM OBTAINS IMAGE OF MOLECULE'S CHEMICAL STRUCTURE

Using an atomically sharp metal tip terminated with a carbon-monoxide molecule, IBM scientists measured the short-range regime of forces that allowed them to obtain an image of the inner structure of a molecule. The colored surface represents experimental data (courtesy IBM Research– Zurich). Using a noncontact AFM (atomic-force microscope), IBM scientists have obtained an image of the chemical structure inside a molecule. The results push the exploration of using molecules and atoms at the smallest scale.

According to IBM, understanding the charge distribution at the atomic scale is "essential for building smaller, faster, and more energy-efficient computing components than today's processors and memory devices." Such components could one day contribute to a "smarter planet" by helping instrument and interconnect the physical world. IBM Research-Zurich scientists Gerhard Meyer, Leo Gross, Fabian Mohn, and Nikolaj Moll worked with Peter Liljeroth of Utrecht University (www.uu/nl) using an AFM in an ultrahigh vacuum at -268°C (-451°F) to image the chemical structure of oblong pentacene molecules comprising 22 1.4-in.-long carbon atoms and 14 1.4-in.-long hydrogen atoms. With the AFM, the researchers looked through an electron cloud to see the atomic backbone of a molecule. For more on this research, go to www.edn.com/article/CA6687056.

IBM Research–Zurich, www.zurich.ibm.com.

# 0.08.09

# **RISE ABOVE**

New Xilinx Targeted Design Platforms give designers a boost to take innovation to a much higher level. These comprehensive platforms combine Virtex<sup>®</sup>-6 or Spartan<sup>®</sup>-6 devices, the ISE Design Suite 11, development hardware, IP, reference designs, documentation, and service and support—so you're way ahead of the competition before you even start. Plus, everything works together seamlessly, so design teams can focus on product differentiation, add more value, and make the whole project more successful. Learn more now at www.xilinx.com/6.

SIGNAL INTEGRITY

### BY HOWARD JOHNSON, PhD

### Real signals

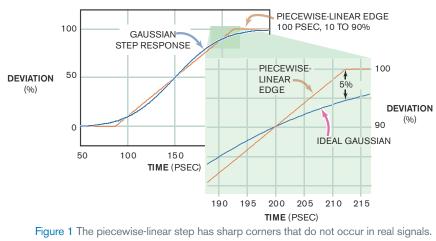

hich step in **Figure 1** best approximates the digital signals you work with every day? The piecewise-linear step starts with a jerk, mindlessly follows a perfectly uniform ramp, and smacks hard into its upper limit. Real signals don't do that. The smooth-look-ing curve is a Gaussian step. It is the time integral of

a Gaussian bell-shaped curve. The Gaussian step has a smooth precursor, a

smooth tail, and a fast, monotonic rise in the middle. It looks more like a real digital signal, and for a good reason.

In the field of linear-system analysis, the Central Limit Theorem states that the step response of any system whose performance is limited by a large number of similar bandlimiting effects tends to become Gaussian as the number of effects approaches infinity. That theorem applies to digital devices because a typical digital driver comprises many performance-limiting stages cascaded in series, all having similar bandwidths.

An I/O driver uses multiple stages to quickly convert nanoamps of cur-

rent from within your silicon into milliamps of current on the PCB (printedcircuit board). A single-stage FET amplifier cannot do that job. If you make a single-stage FET gate big enough to switch PCB-level currents, there is insufficient current available at the silicon level to quickly charge that gate. A better approach breaks down the circuit into a series of multiple stages cascaded in series. Each stage is exponentially larger than the one before it. Gate-design experts spend a lot of time choosing the number of stages within each driver and carefully crafting each stage to achieve maximum performance.

That's where the Central Limit Theorem comes into play. Imagine that you are designing an I/O driver with 10 stages. At dc, the circuit works perfectly. As you go up in frequency, various parasitic effects come into play, limiting the bandwidth. Each stage suffers perhaps 20 parasitic effects, making 200 total effects you must manage to complete the design. The system behaves like a cascade of 200 tiny lowpass-filter elements connected in series. The poorest-performing elements limit the bandwidth of the whole system regardless of how well the other elements work. If you wish to raise the overall performance, attack the worst parts first.

Successively identify the lowesthanging effects and improve them one at a time until you have pushed every part of the system up to a uniform performance ceiling beyond which it becomes increasingly difficult to post significant gains. At that point, stop fiddling and immediately put your product into production. This process creates a system comprising many performance-limiting stages cascaded in series, all having similar bandwidths. For that reason, the step response looks Gaussian.

You can see that the maximum timedomain deviation between a Gaussian step and a piecewise-linear step amounts to only 5% (Figure 1). That amount doesn't sound like much, but those sharp corners in the piecewiselinear curve can induce frequency-domain deviations as large as 20 dB, a significant source of error.EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

+ Go to www.edn.com/091008hj and click on Feedback Loop to post a comment on this column.

+ www.edn.com/signalintegrity

### More measurements. More data. Less cost.

With up to 560 channels of data logging at a maximum scan rate of 1000 channels/sec, an internal 6 ½ digit DMM with 22-bit resolution, and 0.03% accuracy, it's no mystery why Agilent's data acquisition systems are among the top selling in the world. The 34970A and 34980A are both at home with either data acquisition or functional test,

with a broad selection of plug-in modules. Now with Agilent Data Logger Pro software, you'll be able to collect data, check limits, perform extensive branching, and view and store the data without authoring the programming yourself. It's an ideal expansion at a significant savings.

### www.agilent.com/find/daqswitch

Agilent Authorized Distributor

866-436-0887 www.metrictest.com/agilent

SIMPLE IN CONCEPT, VOLTAGE COMPARATORS HAVE MYRIAD SPECIFICATIONS THAT COMPLICATE THEIR APPLICATION.

# COMPARING COMPARATORS: MEASURE SIGNALS, GET RESULTS

BY PAUL RAKO • TECHNICAL EDITOR

lthough humble in concept, today's voltage comparators perform a simple basic task: comparing two voltages to determine which is larger. To accomplish this task, they accept two analog signals and produce a binary signal at the output. In this regard, a comparator resembles a 1-bit ADC. The basic function of a comparator comes in handy in applica-

tions requiring a comparison between a voltage and a stable reference. Such applications include level translation, radar, clock-recovery circuits, wheel sensors on antilock braking systems, precipitation gauges, and headphone-jack detection on handheld products. You can learn about hundreds of other potential applications by reading manufacturers' data sheets and application notes (references 1 through 4). Despite their utility, however, comparators have countless specifications that you must be aware of (**references 5** and **6**), and no single device will make everyone happy. "For 80% of the people, a handful of comparators will fulfill their needs," says Brendan Whelan, design-section leader at Linear Technology. "For the other 20%, no two of them want the same comparator."

Further complicating the selection and application of these devices, some engineers believe that comparators are just op amps running in open-loop configuration-that is, without negative feedback. Because an operational amplifier has a well-balanced difference input and a very high gain, some op amps can serve as comparators in some functions (references 7, 8, and 9). However, in practice, dedicated comparators have several advantages over op amps. For example, dedicated voltage comparators are generally faster than general-purpose op amps that you are using as comparators. A comparator may also contain additional features, such as an accurate internal voltage reference, adjustable hysteresis, and a clock-gated input.

Another reason to choose a comparator over an op amp is that op amps stay within their linear range, whereas comparators run in open-loop mode and switch to a high or a low output. When you use an op amp as a comparator, you must first ensure that no internal clamps lie between the input pins. These clamps prevent you from pulling the input pins more than a diode drop apart. You may be able to overcome these problems by

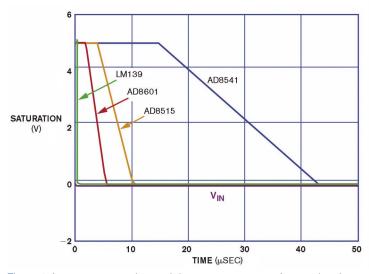

putting series resistors in the op-amp inputs, but that approach raises the input source impedance. Also be aware that op amps may come out of saturation slowly (Figure 1), and, when you drive them to the rails, op amps' quiescent currents may reach excessive levels. And forget about using a handy, "free," leftover op amp from a quad-device package: One part in the quad will swing hard between the rails, almost certainly interfering and causing noise problems with the other three amplifiers in the package. An amplifier's Spice model may also not properly represent a comparator's operation during saturation.

On the other hand, engineers can legitimately use an op amp for a comparator function when their design must discriminate between small voltages of, say, 10 to 200  $\mu$ V. In these cases, an op amp amplifies the input signal to a comparator. In that way, you give the comparator a low-impedance input that provides enough overdrive-the voltage margin above the nominal switching pointto properly switch the comparator. Jim Williams, staff scientist at Linear Technology, has developed several such circuits (references 10 and 11). According to Williams, using an op amp in front of a comparator can also work well. "Take as much gain in the preamp as you can, and let it do the work," he says.

You can also use two comparators to make a window comparator, which indicates whether the input signal is between two levels, or to ensure that the

### AT A GLANCE

Although it has only three pins plus power, a comparator is as tricky to apply as an op amp.

Propagation delay and toggle rate both express the speed of a comparator.

Using an op amp as a comparator can get you into trouble.

Understand all the specs and charts in the data sheet to ensure that your design will work.

To compare microvolt differences, you must use a preamp in front of your comparator.

charging voltage of a lithium-ion charger stays within bounds. Further, you can use comparators with feedback to make free-running oscillators. Because comparators commonly use a reference voltage to set the trip level, hundreds of available parts combine a reference and a comparator.

### **HOW IT WORKS**

The operation of a comparator is straightforward. It has a positive pin and a negative pin. When the voltage on the positive pin is higher, the output of the comparator "asserts," or drives, a signal. With an open-collector output, the comparator's output pin is the collector of a transistor or the drain of a FET. With a push-pull output, the comparator has a "totem-pole" output—that is, a complementary NPN/PNP stage—such as the one you find in operational amplifiers. An open-collector output is useful when the load and the comparator each use a different power supply. This approach allows you to implement, for example, a solenoid operating from 12V, even though your comparator may be operating from only 3.3V. Another use of open-collector outputs is to minimize quiescent current when the output is off. No base current flows in an N-type output transistor, whereas some base current always flows in one of the two output transistors in a totem-pole stage.

Open-collector outputs have a couple of drawbacks, however. For example, they require the use of external pullup resistors. The resistors must perform this pullup during high-impedance periods, so the comparator switches more quickly when its output is low than when it turns off and the pullup resistor brings the output high. Thus, using an opencollector output is unsuitable whenever you need a symmetrical waveform, such as with a clock-recovery circuit. If your circuit requires no level-shifting, you should instead select a push-pull output in a part such as Advanced Linear Devices' ALD2321APC, which can supply a 24-mA output drive and uses 90 µA of quiescent current.

Fast comparators may also have a latched output, allowing you to keep the output in a known state so that you can satisfy a setup-and-hold time to the digital input that it feeds. Once the digital section has read the comparator output,

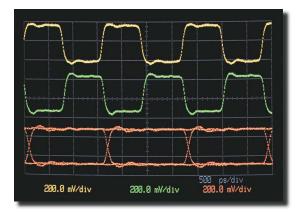

Figure 1 An op amp can take much longer to come out of saturation than a comparator (courtesy Analog Devices).

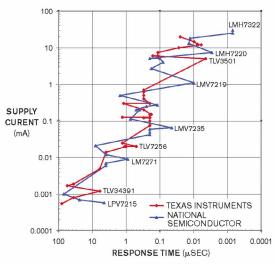

Figure 2 The faster a comparator switches, the more power it consumes.

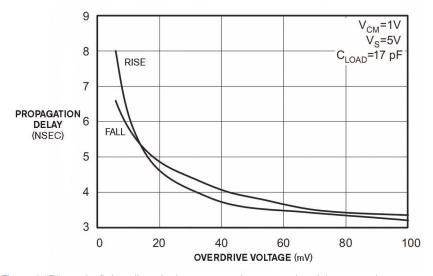

Figure 3 "Dispersion" describes the improvement in propagation delay as you increase the input overdrive (courtesy Texas Instruments).

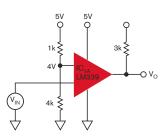

Figure 4 This circuit doesn't work because the comparator has insufficient head room. The inputs are too close to the positive rail.

vou release the latch pin, and the output tracks the input. Fast comparators also may feature ECL (emitter-coupled-logic) levels of -5 to OV. PECL (positiveemitter-coupled-logic) outputs have the same voltage swing but operate at 0 to 5V. RSPECL (reduced-swing-PECL) outputs are also available. Some fast comparators feature LVDS (low-voltage-differential-signaling) outputs with two output pins that shift 300 mV in a complementary fashion around a common-mode voltage of 1.2V. You can run these outputs directly into the LVDS input pins of FPGAs (field-programmable gate arrays) and other digital circuits.

Once you have established the output type, your next likely consideration is speed. Manufacturers generally describe a comparator as either low power or high speed. They typically build the low-power parts with CMOS processes and the fast parts with bipolar devices,

illustrating the fundamental trade-off: fast, accurate parts with high power consumption versus slow parts with lowpower supply currents (Figure 2). Another trade-off is gain versus high speed. A low-power comparator may take 70  $\mu$ sec to switch and use less than 1  $\mu$ A of supply current. A fast comparator with 150-psec response time, such as Analog Devices' ADCMP572, uses 44 mA. Some units stand out in the speed-versus-power trade-off. For example, National Semiconductor's LMV7219 has a 7-nsec propagation delay and uses 1.1 mA; it has relatively low gain, however. In general, an N-type device has higher electron mobility, so it switches from high to low more quickly than it switches from low to high.

A comparator consumes much more than its quiescent power when switching at its maximum toggle rate. In a quiescent state, the current is low. When you push the comparator to operate faster, you must be able to charge the capacitance, which requires current. In dynamic mode, the current increases with the speed of operation. Another factor in power consumption is the load on the chip. Capacitance also presents itself as a load to a switching circuit, and you must account for that capacitance as well as the resistive components of the load. Many parts have shutdown pins that reduce the current consumption to less than 1  $\mu$ A.

As with all things analog, propagationdelay claims are true only under strictly defined conditions because how far apart you drive the input pins directly affects propagation delay. The greater the overdrive, the faster the part is. "Dispersion" is the range of propagation-delay values a device exhibits under varying degrees of overdrive (Figure 3). "Dispersion is a critical spec in ATE [automated-testequipment] systems in which you are trying to measure the propagation delay of a fast logic chip," says Mike Maida, a technologist at National Semiconductor. The relationship between overdrive and speed is the reason that some engineers are loath to rate a comparator's speed as a function of toggle rate. First, you must define the output levels that qualify as a valid transition; an output level of 10 to 90% of maximum is typical. The toggle rate also implies the requirement for a hard overdrive to get the propagation delay to be as short as possible. "Propagation delay is often not a good indicator of toggle rate," says Linear Technology's Whelan. The company offers the LT1719 and LT1715 comparators, both with 4nsec propagation delays and toggle rates of 70 and 150 MHz, respectively.

Another parameter to consider in comparator selection is noise. Manufacturers often omit noise specifications for comparators, however, instead relying on random jitter to measure noise. "In addition to just the noise signal through the gain of the device, the input's aperture errors and the output's rise and fall times can influence the jitter," says Brian Carey, senior design engineer at Analog Devices. "A clock-driver part ... is just a lower-gain comparator that's optimized for noise." National Semiconductor's Maida notes that a designer can use larger input transistors in a CMOS part to reduce flicker noise, but that approach increases the input capacitance.

Once you have selected an output type and satisfied speed and power requirements, your next concern should be the voltage rating of the comparator. Manufacturers once made slow, lowpower devices in CMOS processes, but that approach meant using a 5V power supply; legacy bipolar parts, meanwhile, would work with  $\pm 15V$  supplies. Today, CMOS and BiCMOS analog processes often can achieve power-supply voltages of 12V or more. "In the past, people tended to use bipolar supplies for the really fast comparators because

### Power & Precision Resistors

- Power Resistors

- ecision stors

- Metal Film tor

- Chi

TEPRO

those [devices] used NPN input stages, and they could not extend the commonmode-input range to down to ground," says Maida. National Semiconductor

П

U U U O

implements fast, vertical PNP transistors in the input stage of the LMH7322 so that it can use ground as the negative rail and still allow the inputs to swing 200 mV below ground. Bipolar processes have advantages in supply voltage. Linear Technology's LT1716, for example, has a 44V input and uses only 35  $\mu$ A of power. Many of the company's high-

### VERIFY THE EXACT **PINOUTS OF BOTH** THE OLD PART AND **ITS REPLACEMENT.** EVEN IF THEY COME IN THE SAME TYPE OF PACKAGE.

speed comparators have not only 0 to 5V but also  $\pm$ 5V input capability.

A factor that relates to power-supply range is the permitted common-mode voltage of a comparator's input pins. Many engineers use a legacy LM339 timer from National Semiconductor. However, its manufacturer never intended the part to work with the inputs near

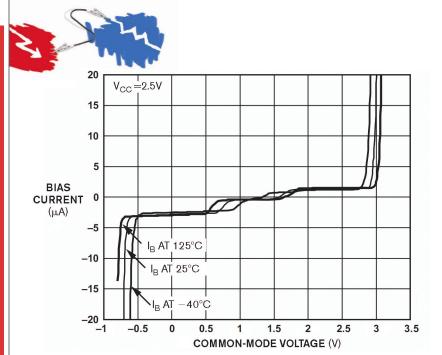

the top power-supply rail (Figure 4). Some parts allow you to drag the outputs above or below the power-supply voltage range, but others invert the output if you drag either input pin below the negative-power-supply rail (Reference 12). A rail-to-rail input-stage comparator, such as Analog Devices' ADCMP60x or STMicroelectronics' TS3021, extends the input-common-mode range. These devices have a dual input stage, with Ntype transistors or FETs in parallel with a P-type input stage. The P-type stage works at input voltages close to ground or the negative rail, and the N-type stage works when the inputs swing close to the positive rail. IC designers usually engineer the devices to switch between stages 1 or 2V below the positive rail. Some architectures minimize the offset voltage, and the most pronounced effect occurs when the input-bias current changes from positive to negative as you sweep thought the common-mode range of a rail-to-rail part, such as Analog De-

Another important spec for comparators is the input-bias current-the amount of current that flows into or out of the input pins as the part operates. CMOS products have low input-bias currents, representing the mismatch in leakages in the input pin's ESD (electrostatic-discharge) structures. This inputbias current doubles for every 10°C of

Figure 5 A rail-to-rail input part has two input stages. With bipolar parts, the input-bias current reverses direction as the input common-mode voltage sweeps through the input range (courtesy Analog Devices).

vices' ADCMP600 (Figure 5).

www.tepro-vamistor.com

**TEPRO** of

FLORIDA, INC.

727.796.1044

**ISO** 9001

temperature rise. The bias currents of fast comparators can be substantial but are not usually problematic because you tend to drive these high-speed comparators with lowimpedance circuits. The input-bias current of bipolar parts changes depending on the relationship of the two inputs. In comparators, a 60mV difference in the base voltage of a differential-input pair yields a 10-times-higher difference in the collector currents of that pair and in the input-bias currents. Thus, you may have one input pin that is sourcing or sinking at twice the rated input-bias current and the other pin with almost no inputbias current, depending on which pin has the higher voltage.

Although designers often overlook it, packaging may be the most critical spec for comparators. Legacy parts have standard pinouts for single and dual comparators that pertain to DIPs (dual inline packages) and SOIC (small-outline-integrated-circuit) packages. You may need one of the newer small packages, such as a SOT-23 (small-outline-transistor) or an SC-70. If you are replacing a legacy part, verify the exact pinouts of both the part and its replacement, even if they come in the same type of package. Other small packages include

solder-bump units, or CSPs (chip-scale packages). These packages are as small as the die itself. Maxim fit the MAX9060 comparator into a four-pin CSP by tying one of the input pins to an internal rail. Some companies don't use CSPs, however, because they can't achieve the low defect rates of other packages. Manufacturers can test CSPs while sorting the wafers but not after they make the solder bumps. Manufacturers can also package parts without bond wires by mounting a solder-bump die to a lead frame. This approach yields parts smaller than  $2 \times 2$  mm and still provides for die protection and product testability.

### **PITFALLS AND PROBLEMS**

All analog circuits have pitfalls, and the comparator is no exception. Application experts report that the two most common design problems are commonmode range and oscillation. To under-

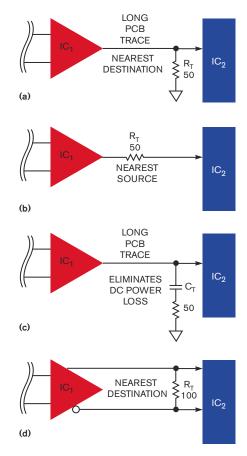

Figure 6 You should terminate fast comparator outputs to prevent ringing and reflections. You can use shunt (a), series (b), ac (c), or differential (d) termination.

> stand common-mode range—the area in which you can operate the input pinsyou must understand the input structure of the comparator you are using. You must take care that your device's input range will not exceed its supply range. To ensure that this scenario does not occur, you should limit or clamp the inputs. You could place a Schottky diode on the LM339's input to ensure that its input cannot go low enough to invert the output. The ESD-protection diodes inside a device clamp the inputs to ensure that the pin cannot go more than 0.6V beyond a power rail. A current of 1 mA is safe, but 10 mA is reaching the

+ Go to www.edn.com/091008df and click on Feedback Loop to post a comment on this article.

+ For more technical articles, go to www.edn.com/features.

### All You Need. One Board.

### NI Single-Board RIO with Processor, FPGA, and I/O

- Embedded real-time processor for stand-alone and reliable operation

- On board FPGA for custom timing and signal processing

- Integrated analog and digital I/O for connecting to sensors/actuators

- NI LabVIEW graphical programming for rapid development

- >> Buy the evaluation kit at ni.com/embeddedeval

800 661 6063

©2009 National Instruments. All rights reserved. LabVIEW, National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2008-10580-305-101-D

upper limit, depending on the duty cycle. ESD-protection diodes on the input pins may limit the voltage, but problems can still occur.

The offset voltage and propagation delay of rail-to-rail devices change as the input levels move from the N-type stage to the P-type stage. In general, this transition is not a problem because you typically set up one of the input pins to a fixed dc level that determines the input stage that will switch the outputs. One important exception is in PWM (pulsewidth-modulated) circuits, in which you feed one pin of the comparator a triangle wave and the other pin a waveform that the PWM represents. In this case, the inputs of the comparator sweep through the entire common-mode range.

Oscillation is the next major headache you may face. The outputs of comparators are high-speed signals no matter how slowly their inputs change. "When the guillotine goes down, it's going to shake the floor," says Paul Grohe, an application engineer at National Semiconductor. In other words, you can expect significant disruption of the power and ground in your circuit if you fail to decouple all your comparators, even the slow ones. Because of these power disruptions, Grohe warns against using a voltage divider on the power rail as a reference for the comparator.

"You have to bypass things really well with micropower parts," says Tim Regan, an application-engineering manager at Linear Technology. "The power-supply rejection is not as good as you might think because you have all these highimpedance nodes inside the part." Fast comparators are even more sensitive to bypassing and board layout (Reference 13). You should maintain a ground plane under the part and ensure that stray capacitances are bringing positive feedback to the inputs to make the part switch solidly rather than create oscillations.

The fundamental way of ensuring clean transitions is to introduce hysteretic resistors into the comparator circuit (Reference 14). These resistors return a bit of positive feedback to swamp out noise and crosstalk once the comparator begins to switch. Without hysteresis, 1 mV of ground bounce can send a part into oscillation, says Brian Hamilton, a design-section leader at Linear Technology. Many fast comparators have built-

### FOR MORE INFORMATION

Advanced Linear Devices www.aldinc.com Analog Devices www.analog.com Linear Technology Corp www.linear.com Maxim Integrated Products www.maxim-ic.com National Semiconductor www.national.com On Semiconductor www.onsemi.com Rohm Semiconductor www.rohm.com STMicroelectronics www.st.com Texas Instruments www.ti.com

in hysteresis, and some have a pin that lets you select an adjustable hysteresis level

Another problem with comparators is high source impedance, which makes your circuit prone to oscillation and subject to crosstalk and stray capacitance. Bob Gonzalez, an applications engineer with On Semiconductor, warns against placing 10-k $\Omega$  resistors in series on the inputs because this approach increases impedance into the inputs. The devices have internal parasitic capacitance; if the input impedance is high, that capacitance becomes prominent and adds phase shift to the circuit, leading to oscillations. You may want to use an opamp buffer or a simple emitter-follower transistor circuit in front of the comparator to minimize the source impedance. You may also be able to overcome the problem by adding hysteresis.

Proper termination of outputs and maintaining an appropriate temperature are also critical factors in avoiding problems with comparators. Hooking a device's output to a long transition line may cause reflections from the end of the line unless you provide for a termination. You might consider an RC-termination network if you do not want to waste dc power. You could also look at using series termination that allows a reflection from the destination but then absorbs it in a series resistor (Figure 6).

The performance of a comparator changes over temperature. IC designers have made great strides in this area, though, so many parts are available that meet specifications over -40 to +125°C. Still, comparators are prone to oscillate at low temperatures, and high temperatures lower the device's base-to-emitter voltages and cause other performance differences. It is essential to evaluate your circuit at all the temperature extremes it will face in service.

"The biggest thing is propagation-delay change with temperature," says National Semiconductor's Maida. "It tends to be faster cold and slower hot. The common-mode range also shifts a little over temperature. In general, gain tends to get worse going hot, and it's more of a design challenge for head room."

Another concern is whether to simulate your circuits using Spice models. Most company representatives admit that older Spice models are far less reliable than new ones. Texas Instruments is committed to making good models for all its comparators and offers the free Tina-TI model, which allows you to cut and paste all schematics and waveforms as metafiles into Word or PowerPoint. Remember that, when you are dealing with fast comparators, the PCB (printed-circuit board) is an important component in the design; your layout may create stray capacitances and crosstalk, and these effects will overshadow any Spice simulation that does not model these second-order effects. The extreme speed of Analog Devices' new comparators, for example, causes problems for Spice. "We do not have Spice models for our newer parts because, as you go higher in performance, it becomes more difficult to get a reasonable model," says James Frame, a marketing manager at Analog Devices, which is considering developing models. The company will release them only if they are sufficiently accurate, however, so as to not mislead its customers, he says.

Over the years, the processes for manufacturing comparators have improved. Advanced CMOS processes have low power consumption and operate at more than 5V. The fast parts can take advantage of vertical PNP transistors, and the fastest have the benefit of SiGe (silicon germanium, **Reference 15**). "If you get to mix and match processes, there are obvious parts of a comparator that make sense for you to do in different processes," says Linear Technology's Hamilton.

Analog Devices uses a SiGe process in its high-speed comparators. "SiGe has a better speed-power product but also better gain; you just can't get high gain out of CMOS; we've tried," notes Carey. SiGe also has a greater voltage range. "You can't give people a 1.8V-input-range comparator; everyone wants to put in at least 2 or 3V along with a wide common-mode range on these parts," he says. Analog Devices also uses dielectric isolation to make some of the fastest comparators available. Dielectric isolation in the company's XF3 process provides low parasitic capacitance and low leakage currents.

With thousands of comparator parts and even more application circuits, you may feel overwhelmed. Armed with the basics and the subtleties, however, you can sift through all the specifications to find the comparator that provides the optimum trade-off among all your requirements. Whether you are trying to detect a pushbutton on a handheld product or sensing the trigger level in a gigahertz-frequency input to an oscilloscope, a comparator exists to fill the bill. Just heed Gordon Holton, strategic-marketing manager at Texas Instruments, when he warns you not to be too cheap. He notes some customers buy the lowestcost comparator only to find they need the rail-to-rail input of a better part. The manufacturers' Web sites will help you

# **GAIN Experience. SAVE Time.**

Your Power Questions Answered in the Lab

EMI: How to Get the Lowest Noise

**Thermal & Mechanical Considerations**

**Input Overvoltage Protection**

Improving Output Filtering

Vicor's PowerTechtorial Series concentrates on important, real-world technical issues in power system design. Power questions are answered by senior applications engineers through concise, expert instruction in the lab. Gain access to view an ever-growing number of Vicor PowerTechtorial videos at vicorpower.com/PT3.

Vicor Applications Engineering: 800-927-9474

winnow the parts, and their applicationengineering staffs will keep you out of trouble. By embracing the unique combination of analog and digital characteristics in a comparator, you can make sure you get the most from your circuits.**EDN**

### REFERENCES

"Specifying Selected Op Amps and Comparators," Linear Brief 26, National Semiconductor, October 1973, www. national.com/ms/LB/LB-26.pdf.

"LM139/LM239/LM339: A Quad

of Independently Functioning Comparators," Application Note 74, National Semiconductor, January 1973, www. national.com/an/AN/AN-74.pdf.

Applications of the LM392 Comparator Op Amp IC," Application Note 286, National Semiconductor, September 1981, www.national.com/an/AN/ AN-286.pdf.

Williams, Jim, "A Seven-Nanosecond Comparator for Single Supply Operation," Application Note 72, Linear Technology, May 1998, http://cds.linear. com/docs/Application%20Note/an72f. pdf. "Comparators," MT-083 Tutorial, Analog Devices Inc, 2009, www.analog. com/static/imported-files/tutorials/ MT-083.pdf.

Mancini, Ron, "Designing with comparators," *EDN*, March 29, 2001, pg 56, www.edn.com/article/CA69100.

"Using Op Amps As Comparators," MT-084 Tutorial, Analog Devices Inc, 2009, www.analog.com/static/ imported-files/tutorials/MT-084.pdf.

Moghimi, Reza, "Amplifiers as Comparators?" Analog Dialogue, April 2003, www.analog.com/library/ analogdialogue/archives/37-04/ comparator.pdf.

"Microvolt Comparator," Linear Brief

32, National Semiconductor, June

1976, www.national.com/ms/LB/

LB-32.pdf.

Williams, Jim, "Application Considerations and Circuits for a New Chopper-Stabilized Op Amp," Application Note 9, Linear Technology, http://cds.linear.com/docs/Application%20Note/an9.pdf.

Williams, Jim, "A Seven-Nanosecond Comparator for Single Supply Operation," Application Note 72, Figure 65, Lin-

ear Technology, May 1998, http://cds. linear.com/docs/Application%20Note/ an72f.pdf.

<sup>12</sup> "LM139/LM239/LM339/LM2901/ LM3302 Low Power Low Offset Voltage Quad Comparators," Note 3, National Semiconductor, March 2004, www.national.com/ds/LM/LM139.pdf. <sup>13</sup> Williams, Jim, "High Speed Comparator Techniques," Application Note 13, Linear Technology, April 1985, http://cds.linear.com/docs/ Application%20Note/an13.pdf. <sup>14</sup> Mancini, Ron, "Adding hysteresis to comparators," EDN, May 3, 2001, pg 22, www.edn.com/article/CA84881. <sup>15</sup> Rako, Paul, "Silicon germanium: fast, quiet, and powerful," EDN, Sept 18, 2008, pg 27, www.edn.com/article/ CA6594090.

You can reach Technical Editor Pau Pake at 1-408-745-1994 and paul.rako@ edn.com.

### THE CADENCE OrCAD DIFFERENCE IS DEPTH

18<sup>0</sup> A10 A10 19 **BK0** A11 20 <u>BK1</u> A12 21 BK2 A13 22 BK3 A14 23 BK4 A15 WE 11

**New OrCAD Release 16.2** delivers unparalleled depth and robust functionality with innovative features like the new "fisheye" view that makes dense designs edit like small designs.

**Test Drive OrCAD Release 16.2.** For a free demo DVD, visit EMA Design Automation, a Cadence<sup>®</sup> Channel Partner, at www.ema-eda.com/demoDVD or call us at 800.813.7288.

cādence™

# Boldly go where no system has gone before....

Pico-ITXe

ALC TANK

Pico-I/O

EPIA-P740 Pico-ITX9" Mainboard

- Revolutionary Pico-ITXe<sup>™</sup> Embedded Form Factor (100mm x 72mm) with PCIe, USB, & LPC Interfaces

- VIA C7 1.0GHz Processor Driving SUMIT<sup>™</sup> I/O

- Supports 10/100/1000 Gigabit Ethernet

- ACCES Pico-I/O<sup>™</sup> Boards (72mm x 60mm) for Stacking and System Design Flexibility

### Digital IIO, 8 Form C Relays and 16 TTL/LVTTL IIO Lines

3.775" (96mm

PC/104

PICO

**Pico-I/O** Exactly <sup>1</sup>/<sub>2</sub> the size of

PC/104!

2.835" (72mm)

VIA Technologies' tiny Pico-ITXe<sup>™</sup> SBC combines with ACCES I/O Products' Pico-I/O<sup>™</sup> boards for the latest small size OEM embedded system standard.

SUMIT<sup>™</sup> standard provides a multitude of high speed and low-cost stacking I/O interfaces. Serial and low pin count I/O allows for smaller interface connectors for design and space savings. Push the limits for mobile low power systems -

### **Explore the Possibilities!**

**Pico System**

To find more information on EPIA mainboards, please visit www.VIAembedded.com or call 510 683 3300. Come visit us at 940 Mission Court Fremont CA 94539

To learn more about our Embedded Pico-I/O<sup>w</sup>boards visit www.accesio.com or call 800 326 1649. Come visit us at 10623 Roselle Street San Diego CA 92121

### Saving Space, ne Final Frontier

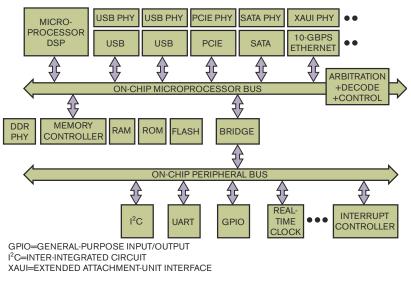

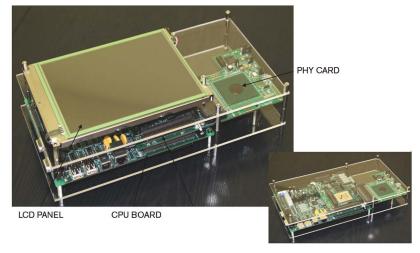

One of the responsibilities of board-level designers is to ensure that verification and failure-analysis engineers have adequate access to signals without resorting to drills, bed-of-nails testers, or focused ion beams. This requirement used to be simple when pads were farther apart, chips were less complex, and signals were more robust. Today, however, design for debugging is a major concern for creators of board-level products. Some signals-especially in high-speed serial interfaces-are virtually unprobable. Some are inaccessible in the fine-pitch tangle beneath highpin-count chips. SOCs (systems on chips) lock within themselves some vital information. And some nets that used to require only occasional glances—power and clock networks, for example—have transformed under the pressure of advanced power-management techniques into signal nets that require functional verification. Today, design for debugging requires a plan and a systematic design approach from the beginning of the project.

Q

# DESIGNING AN ACCESSIBLE BOARD

DESIGN IN ACCESS TO VERIFICATION AND DEBUG-GING DURING—NOT AFTER—THE DEVELOPMENT OF A BOARD-LEVEL PRODUCT.

BY RON WILSON EXECUTIVE EDITOR

0.000000

This undertaking is not just another version of design for test. Test engineers want the quickest possible answer to one question: Can I ship this board? Verification and failure-analysis engineers have a different problem. They must be able to put the board through a sequence of states while observing its behavior, and, if the behavior is wrong, they must trace the problem back to its source. This requirement is far more demanding.

Reference designs, because they must be both accessible to the customer and nearly production-ready, present excellent studies for understanding how designers approach this problem. Video-processing vendor Stretch Inc, for example, is acutely aware of the challenge-and opportunity-of referencedesign boards. "The reference design is more like an end product," says Ashish Thanawala, director of systems engineering at the company. "We share it with our customers, who want to take it to market as quickly as possible, and so they care about the size of the board. For that reason, we don't put in test points."

On the other hand, access to the refer-

### AT A GLANCE